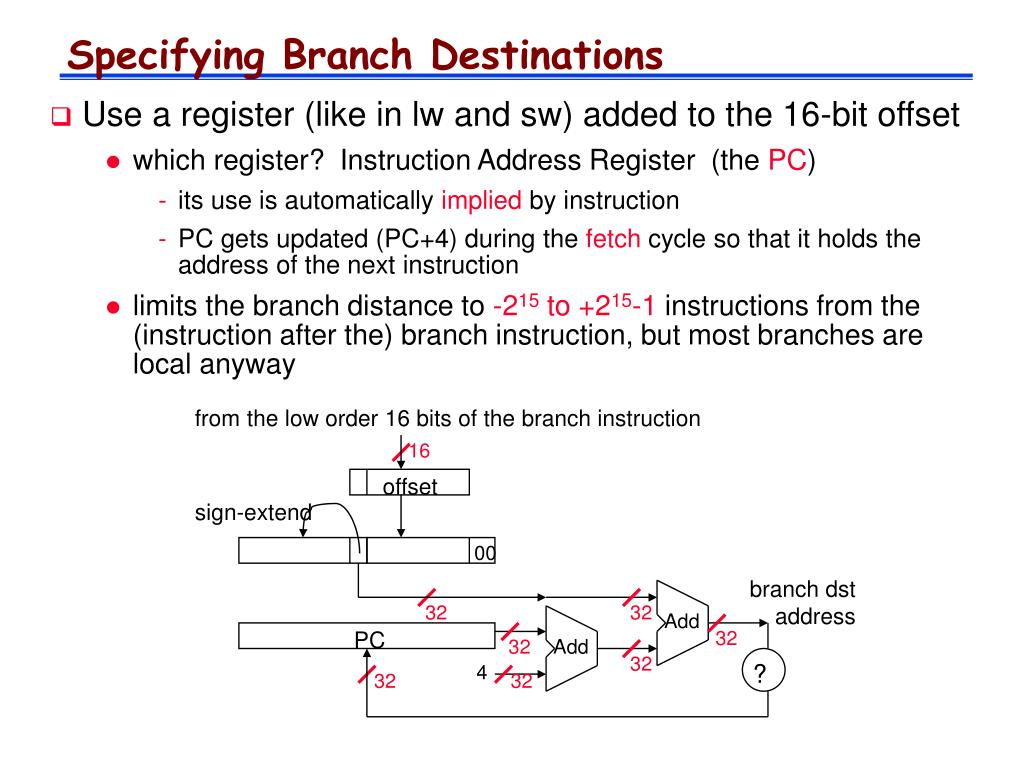

We need addressability thus: the I - type instructionĩ I - Type instructions op 6 BITS rs 5 bits rt Immediate address 16 bits Not enough bits in a 32 bit instruction to directly give a full address.

#Beq mips maximum jummp distance code#

R-TYPE FIELD MEANINGS op - the basic op-code of the instruction rs - first register source operand (ex: $17 above) rt - second register source operand (ex: $18 above) rd - register destination operand (ex: $8 above) shamt - shift amount - more later funct - function field - variations of the op code op 6 bits rs 5 bits rt rd shamt FunctĨ Memory Instructions We can’t work only with registers forever - sooner or later we must access memory this necessitates a different instruction type I - Type instructions - an op code and three operands Needed for moving data between register and memory Can’t treat memory cells like registers - too many of them. Good design demands compromise A limited variation in format is desirable to optimize performance - three types of related instruction formats Make the common case fast Allow immediate data in the instruction and implement it efficiently Remember Amdahls Law!Ħ MIPS INSTRUCTIONS MIPS instructions consists of fixed sized fields, with a minimal variation (3) of formats Notation: $n, where n = 0, 1, 2, represents a general purpose register number n Example: add $8, $17, $18 # $8 = $17 + $18 sub $8, $17, $18 # $8 = $17 - $18 Note: everything after # sign is a comment (like “ ” for Intel) An alternate symbolic designation may also be used for registers (see page A23 for the correspondence) – this may be the preferred notation for real programs even though the above notation also works. Smaller is faster register are faster - use a lot of them - but too many will slow things down - 32 (64) may be the limitĥ Four Basic RISC Principles In Designing An Instruction Set (Cont.) Simplicity favors regularity Minimal number of instruction formats and a only a fixed number of operands within a format (three for arithmetic). Implementation uses pipelining and cache principlesĤ Four Basic RISC Principles In Designing An Instruction Set Instruction format relatively fixed Only three closely related types permitted Heavy reliance on large number of general purpose registers Only two instructions use memory: load (lw) and store (sw) all other operations are done using registers. name based on the performance metric: “millions of instructions per second” based on an experimental system developed at Stanford by Hennessy MIPS architecture and instruction set is typical of RISC designs designed since the early 80's similar to the Sun Sparc processor MIPS will be the basis of our study approach: first understand the instruction set (architecture seen by the programmer) and then design the underlying hardware to implement the instructions.ģ Some Basic Features Characteristic of RISC Principles MIPS is a family of RISC processors developed by mips computer company. Guydosh 2/2/04+Ģ MIPS Approach MIPS will be the basis of our study 1 CS325 Instructions: Language of the Machine MIPS ARCHITECTURE - AN INTRODUCTION TO THE INSTRUCTION SET by N.

0 kommentar(er)

0 kommentar(er)